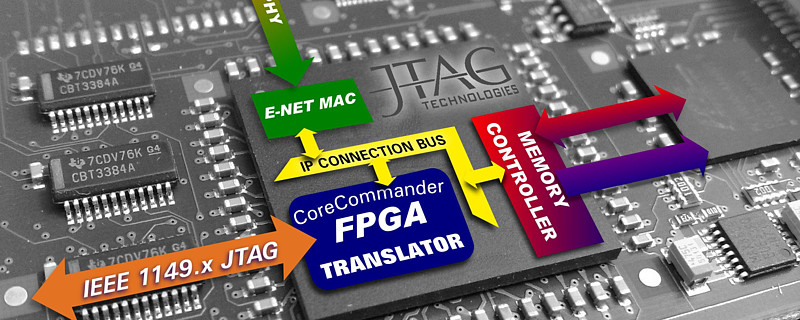

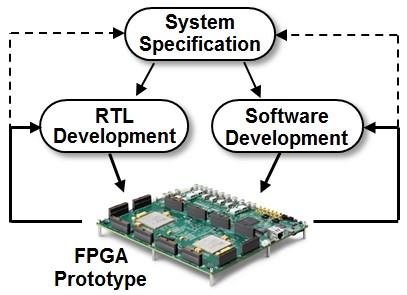

FPGA是Field Programmable Gate Array的简写,中文全称为现场可编程门阵列。FPGA的设计包括软件设计和硬件设计两大块。软件设计包含嵌入式C程序和HDL程序设计,嵌入式C程序是最近才开始流行的。硬件设计,顾名思义就是与硬件相关的,包括电路设计、配套硬件设计、输入输出接口设计等。

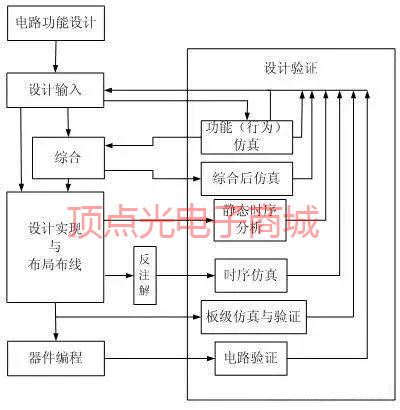

FPGA的开发离不开EDA开发软件和编程工具,开发流程按照先后顺序,依次为电路设计、输入设计、功能仿真、综合优化、综合后仿真、实现、布线后仿真、板级仿真和芯片编程、调试等。

一、方案验证

在开始所有步骤之前,一定要进行方案验证。工程师会根据项目要求,对整个系统进行综合考量,包括各项指标、复杂程度,FPGA芯片的工作速度、成本、供货渠道等。方案验证通过之后,就需要进行系统设计和FPGA芯片选择等筹备工作。

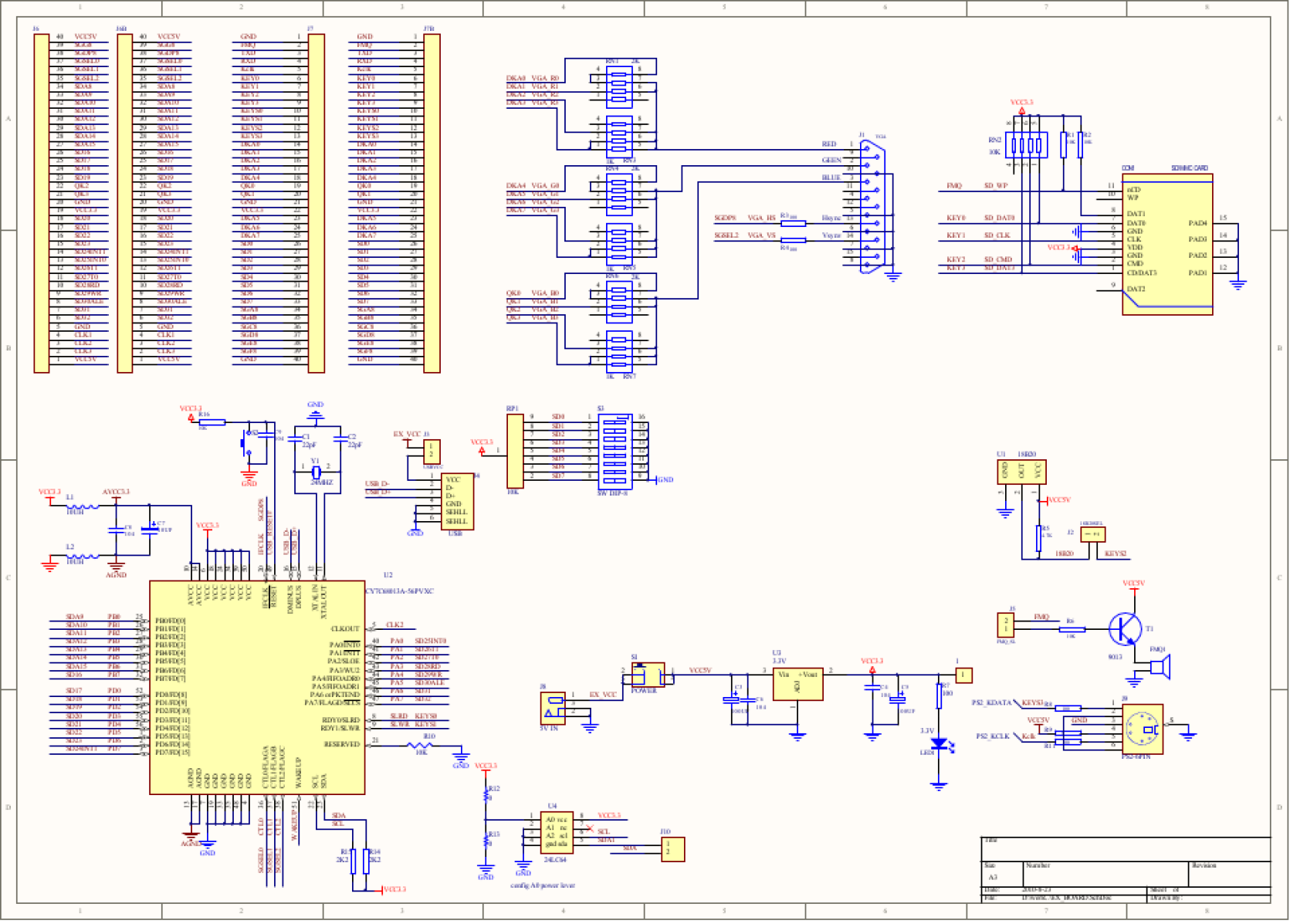

二、电路设计

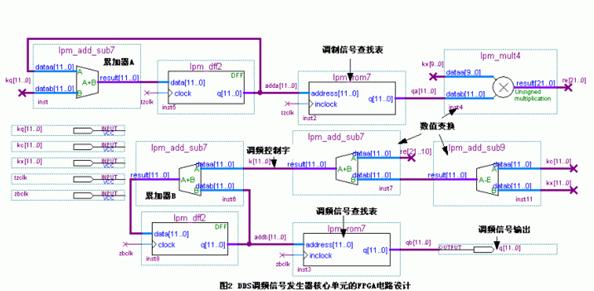

FPGA电路设计通常都是采用金字塔式的逻辑,自上而下进行的。首先需要把整个系统划分成各个基本单元,然后再把各个单元进行细化、分层,直到可以直接使用EDA器件库。

三、输入设计

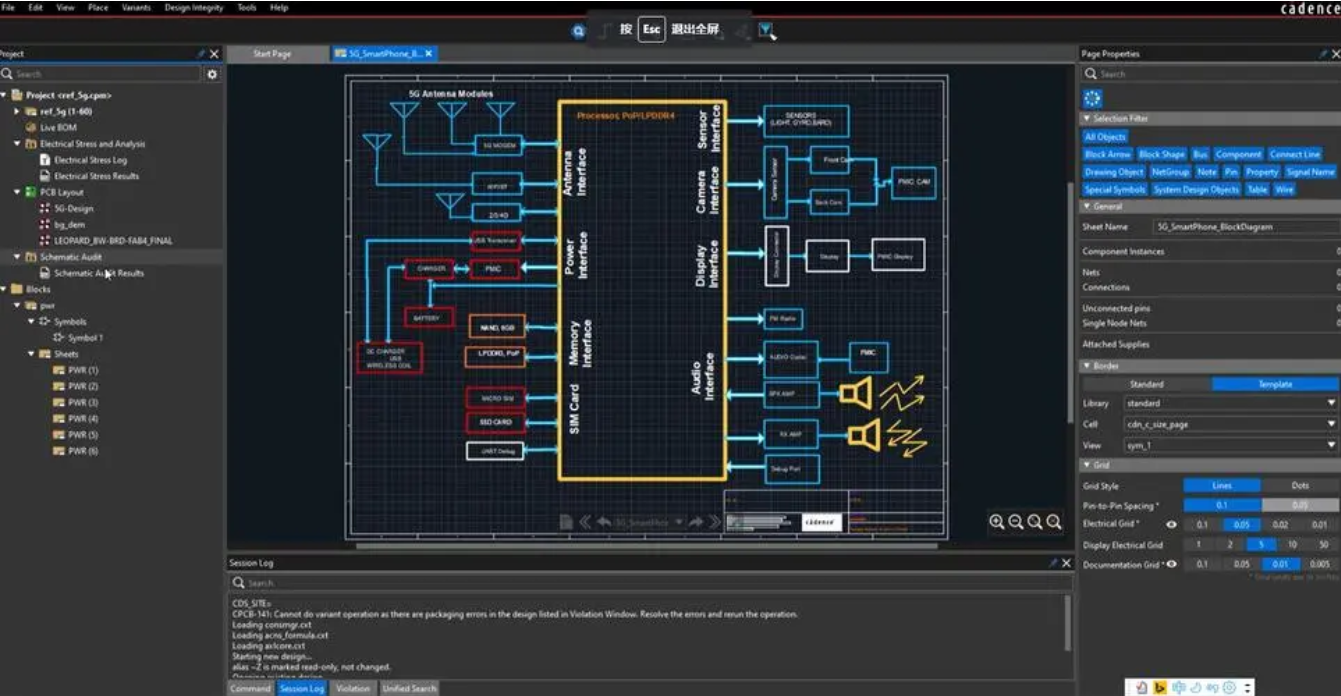

输入设计就是将系统电路按照开发软件的规范进行表达,使EDA工具能够直接进行操作。输入设计的主要方法主要包括原理图输入法和硬件描述语言(HDL)法。其中,原理图输入法是最直接的表达方式,在早期FPGA芯片的发展过程中,就被广泛应用。原理图输入法从元器件库中,将所需的器件全部调出,然后进行原理图的绘制。

原理图输入法的优点是直观易懂,并且仿真很便捷;缺点是维护起来比较麻烦,涉及到模块的构造和重用时,篇幅会大量增加,特别是需要进行系统升级时,基本上所有的原理图都要进行适当修改,整体效率偏低。

随着各项指标要求的演变,硬件描述语言(HDL)法逐渐成为现今开发中应用最广泛的方法。HDL法根据文本描述设计,又可以分为行为HDL和普通HDL。

行为HDL主要用在大型工程中,主流语言是VHDL和Verilog HDL,采用的是IEEE(美国电气与电子工程师)标准,其共同特点是利于自上而下的设计,语言与芯片工艺无关,可移植性好,有很优秀的仿真和逻辑表述功能,输入效率高,便于模块划分和移植。

普通HDL主要用于小型设计,包括CUR和ABEL,支持状态机、逻辑方程和真值表等方式。

四、功能仿真

功能仿真又称为前仿真,仅对初步的功能进行验证,没有延迟信息,只是对所设计的电路进行逻辑功能验证。在仿真前,需要将核心的输入信号进行序列组合,也就是利用HDL和波形编辑器建立测试向量和波形文件。仿真结果以信号波形和报告文件的形式呈现,方便观察各个信号节点的变化情况。如果出现错误,就返回修改逻辑设计。

五、综合优化

综合优化,简单来说就是将高级抽象描述转化为具体详细的描述,根据目标要求对所生成的逻辑连接进行优化,使设计层次更加平面化,以便实现FPGA布局布线。

从层次上来看,综合优化主要是将输入设计编译成逻辑连接网表,以便和触发器、RAM、与或非门等基本逻辑单元进行连接。真实具体的门级电路还要利用FPGA制造商的布局布线功能,再根据综合后的逻辑连接网表来绘制,也就是标准门级结构网表。因此,综合优化并非最终的门级电路。

另外需要注意的是,为了确保标准门级结构网表的转换,在编写HDL程序时,必须要针对特定综合器的风格进行匹配。

六、综合后仿真

综合后仿真,是检查综合结果与原设计是否一致的步骤,通过把综合生成的标准延时文件,反标注到综合仿真模型中,来对门延时影响进行评估。该步骤并不能对线延时进行评估,因此和布线后的实际情况有差距。

现阶段综合工具已经比较成熟,对于一般的设计而言,通常这一步骤可以省略。但是,如果布局布线之后,出现电路结构与设计意图不符的情况,还是需要通过综合仿真来查找问题根源。

七、实现与布局布线

实现,就是将综合生成的逻辑网表在FPGA芯片上进行配置,完成布局布线。展开来说,布局是将逻辑网表中的硬件与底层单元,在FPGA芯片内部的固有硬件结构上进行合理的配置,以便达到最优的面积和最优的速度。布线则是在布局拓扑结构的基础之上,结合FPGA芯片内部的各种接口,准确连接各个元器件。由于布局布线需要用到FPGA芯片内部的所有硬件和接口,因此必须选择FPGA芯片原厂提供的工具。

由于FPGA的结构十分复杂,尤其是在时序约束条件下,必须要用到时序驱动引擎来完成布局布线。完成布线之后,软件工具可以自动生成报告,展示设计中各资源的使用情况。

八、后仿真

后仿真,也叫时序仿真,主要是将布局布线后的延时信息,反向标注到设计网表中,以便检查是否有时序违规存在,比如保持时间、建立时间等是否满足器件的固有时序规则或时序约束条件。

后仿真可以精确、完整的展示延迟信息,因此能很好的反馈芯片时间工作时的情况。

后仿真的意义重大。因为不同FPGA芯片的内部延时不同,布局布线方案也会给延时造成影响。因此,在完成布局布线之后,对整个系统以及各个模块进行后仿真,可以验证时序关系、评估系统性能,对检查和消除设计风险具有重大意义。

九、板级仿真及验证

在高速电路设计中,还需要进行板级仿真。板级仿真主要是对高速系统的电磁干扰和信号完整等指标进行检查,通常采用第三方工具进行。

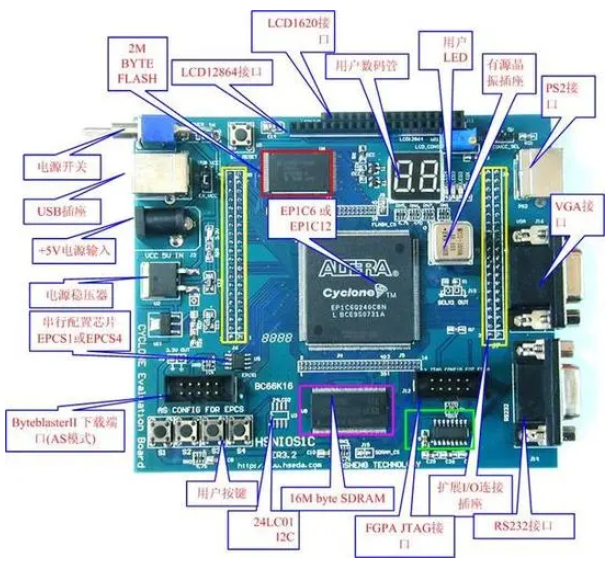

十、编程与调试

芯片的编程与调试是整个FPGA开发流程的最后一步。芯片编程需要先生成使用所需的数据文件,即位数据流文件,然后再将数据文件上传到FPGA芯片内。

芯片编程需要在一定的条件下进行,比如编程时序、编程算法和编程电压等。在FPGA的设计过程中,逻辑分析仪是一种重要的调试工具。逻辑分析仪价格比较贵,且需要引出大量的测试管脚。不过,主要的FPGA芯片厂家都会提供内嵌的逻辑分析仪,比如Xilinx赛灵思内嵌的ChipScope和Altera阿尔特拉内嵌的SignalTapII、SignalProb等。

通过厂家内嵌逻辑分析仪,可以帮助客户降低成本,同时减小FPGA芯片逻辑资源的占用,实用性非常强。

鄂公网安备 42011502001385号 鄂ICP备2021012849号

鄂公网安备 42011502001385号 鄂ICP备2021012849号