顶点光电子商城2024年5月20日消息:近日,台积电准备生产HBM4基础芯片,并将采用N12FFC+和N5制程技术。这一决策是为了满足当前人工智能(AI)市场对高性能存储的需求。

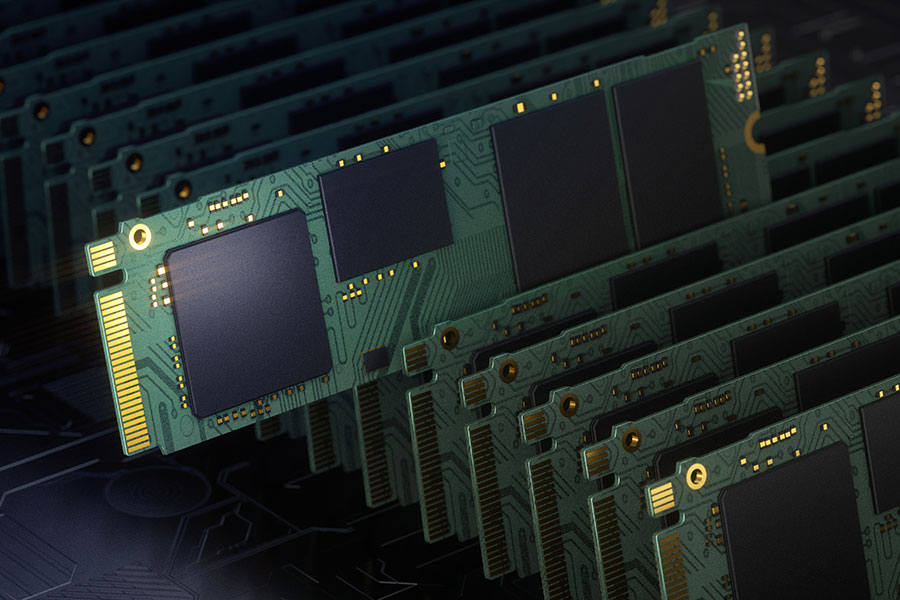

HBM4,即第四代高带宽内存,相较于之前的HBM产品,有几项主要的变化。其中,最重要的就是内存堆栈链接接口标准,将从原本的1024比特进一步转向超宽的2048比特。这种变化使得HBM4内存堆栈链接需要更先进的封装方法来容纳超宽的内存。

在制程技术方面,台积电计划使用N12FFC+和N5两种制程技术来生产HBM4基础芯片。N12FFC+是一种成本效益较高的选择,它可以使存储供应商构建12层堆栈(48GB)和16层堆栈(64GB),每堆栈带宽超过2TB/s。此外,N12FFC+技术生产的HBM4基础芯片还有助于使用台积电的CoWoS-L或CoWoS-R先进封装技术构建系统级封装(SiP),该技术可提供高达8倍标线尺寸的中介层,空间足够容纳多达12个HBM4内存堆栈。

另一方面,N5制程技术则提供了更高的性能。N5制程建构的基础芯片将封装更多的逻辑,消耗更少的功耗,并提供更高的性能。这种先进的制程技术可以达到非常小的互连间距,约6~9微米,这将使得HBM4能够在逻辑芯片顶部进行3D堆栈,从而提高内存性能。

总的来说,台积电采用N12FFC+和N5制程技术生产HBM4基础芯片,是为了在保持成本效益的同时,提高存储性能,满足AI和高性能计算(HPC)芯片对更大内存带宽的需求。

鄂公网安备 42011502001385号 鄂ICP备2021012849号

鄂公网安备 42011502001385号 鄂ICP备2021012849号